第四节 4000系列CMOS数字集成电路(七至十二)

本节将继续介绍4000系列CMOS数字集成电路中的六款经典芯片,涵盖计数器、触发器、锁存器等重要逻辑功能部件。这些芯片以其低功耗、宽工作电压范围和良好的抗干扰能力,在早期及许多对功耗敏感的数字系统中得到了广泛应用。

七、CD4029:可预置二进制/十进制加/减计数器

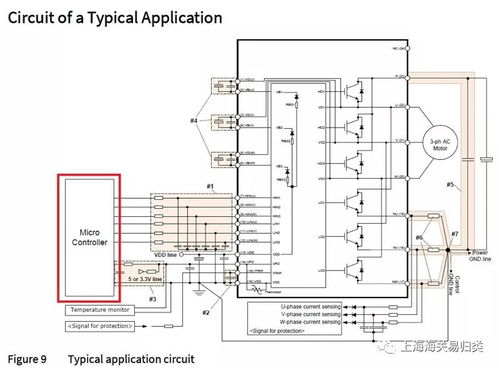

CD4029是一款功能灵活的可预置同步计数器。它既可作为二进制计数器(模16),也可通过模式选择作为十进制计数器(模10),并且能进行加计数或减计数。其预置功能允许用户通过并行数据输入端(P0-P3)设置初始计数值,当预置使能端(PE)有效时,将数据载入计数器。时钟输入端(CLK)在上升沿触发计数。进位/借位输出端(CO/BO)在加计数达到最大值或减计数达到最小值时产生脉冲,便于级联构成多位计数器。CD4029常用于频率合成、数字定时、顺序控制等场合。

八、CD4040:12位二进制串行计数器

CD4040是一个12级纹波计数器(异步计数器),由12个负边沿触发的T型触发器串联构成。它有一个公共的时钟输入端(CLK)和一个公共的异步复位端(RESET)。每当时钟信号出现下降沿时,计数器递增。其12个输出端(Q1-Q12)分别提供2分频、4分频直至4096分频的方波信号。由于其异步工作方式,中间级的输出存在微小的时间延迟(纹波),因此在需要严格同步的系统中需注意。它主要用于分频、定时以及需要长计数周期的应用。

九、CD4042:四D锁存器

CD4042包含了四个独立的D型锁存器,每个锁存器有一个数据输入端(D)、一个输出端(Q及其反相输出Q’)以及一个公共的时钟极性选择端(POL)。锁存器的动作由时钟信号(CLK)控制。当POL为高电平时,CLK为高则锁存器透明(输出随输入变化),CLK变低则锁存数据;当POL为低电平时,逻辑相反。这种设计增加了使用的灵活性。四D锁存器常用于临时存储数据、消除开关抖动、以及作为简单的数据缓冲器。

十、CD4043/4044:四三态R-S锁存器

CD4043和CD4044均包含四个独立的置位-复位(R-S)锁存器,并带有三态输出功能。两者的主要区别在于逻辑类型:CD4043采用或非门结构(高电平触发置位/复位),而CD4044采用与非门结构(低电平触发置位/复位)。每个锁存器有S(置位)和R(复位)输入端,以及一个使能端(EN)。当EN有效时,输出根据R、S状态变化;当EN无效时,输出呈高阻态,允许总线共享。它们特别适用于消除机械开关抖动、作为简单的状态存储单元以及在总线系统中进行数据暂存。

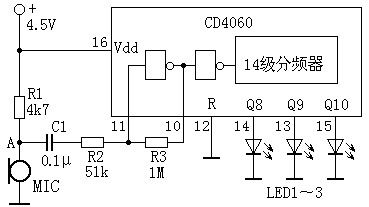

十一、CD4047:单稳态/无稳态多谐振荡器

CD4047是一款多功能振荡器/定时器集成电路,既可以作为单稳态触发器(产生固定宽度的脉冲),也可以作为无稳态多谐振荡器(产生连续的方波信号)。工作模式由外部连接方式决定。它内置了基本的振荡和定时电路,通过外接一个电阻和两个电容(或一个电阻一个电容,取决于模式)来设定时间常数,从而控制输出脉冲的宽度或振荡频率。CD4047具有一个触发输入端(-TR)、一个重触发输入端(+TR)、一个复位端(R),以及互补的输出端(Q和Q’)。它常用于脉冲整形、延时产生、方波信号发生和频率调制等。

十二、CD4050:六同相缓冲器/电平转换器

CD4050集成了六个独立的同相缓冲器/驱动器。每个单元具有高输入阻抗和一定的电流驱动能力。除了基本的缓冲和驱动功能外,CD4050一个非常重要的特性是能够进行不同逻辑电平之间的转换,尤其是在单一电源电压(如5V)供电下,其输入端可以耐受比电源电压(VDD)更高的电压(例如12V或15V),从而能够安全地与更高电压的逻辑系统或器件接口。这使得它在混合电压数字系统、驱动LED、继电器或作为总线驱动器时非常有用。

****

从灵活可编程的计数器CD4029,到长分频的CD4040,再到数据锁存与存储的CD4042、4043/4044,以及定时振荡的CD4047和接口缓冲的CD4050,这六款芯片展示了4000系列CMOS集成电路在数字系统基础功能构建上的多样性和实用性。尽管当今高性能、高集成度的CPLD、FPGA和微控制器已非常普及,但理解这些基础的中小规模标准集成电路,对于掌握数字电路的根本原理、进行快速原型验证以及在特定低功耗、高可靠性的简单应用中,仍然具有不可替代的价值。

如若转载,请注明出处:http://www.sh-srs.com/product/24.html

更新时间:2026-04-23 20:38:37